接続テスト(或いはインターコネクトテスト)は、あらゆるテストスイートにとって不可欠な機能で、“部品が適切に基板上に半田付けされているか?”と“回路内に短絡箇所が無いか?”をチェックします。

より向上された接続テスト

XJTAGの接続テストは、(短絡・断線・スタックの)3種類の基板上の不具合を検出します。その上、他の接続テストで同じ種類の不具合が発見されれば、XJTAGは発見された不具合と詳細な発生場所を表示します。

ATPG “オンザフライ”の自動テストパターン生成

XJTAGの接続テストは、実行の度にテストパターンを生成します(Automatic Test Pattern Generation – ATPG) 。 そのためツールベンダーなどによる新しいテストパターンの開発は必要なく、基板のあらゆる設計変更に簡単に素早く対応できます。

レジスタ越しのテスト

この図は、大多数のJTAG接続テストで問題となる状況を示しています。殆どの従来の接続テストで用いられているアルゴリズムでは、NetCとNetDの 短絡は検出できますが、NetAとNetBの様に直列抵抗を介した短絡は検出できません。XJTAGの接続テストアルゴリズムはこの問題を解決します。

標準としての診断機能

すべてのシステムの標準部品として提供される高精度の障害分離診断は、検出された障害の種類、関連するネットおよびピンを強調表示し、基板のレイアウトと回路図へのリンクを提供して、ボードの修理を支援します。

XJTAGとテストシステムを統合する

XJTAGのソフトウェア、ハードウェアは、他のテストシステムやツールと統合できます。

これらの統合機能は、既存のシステム内でXJTAGを使用すること、あるいはXJTAGをベースに他の機器を統合するなど、必要なテストシステム全体を構築する柔軟性を提供します。

ソフトウェアの統合

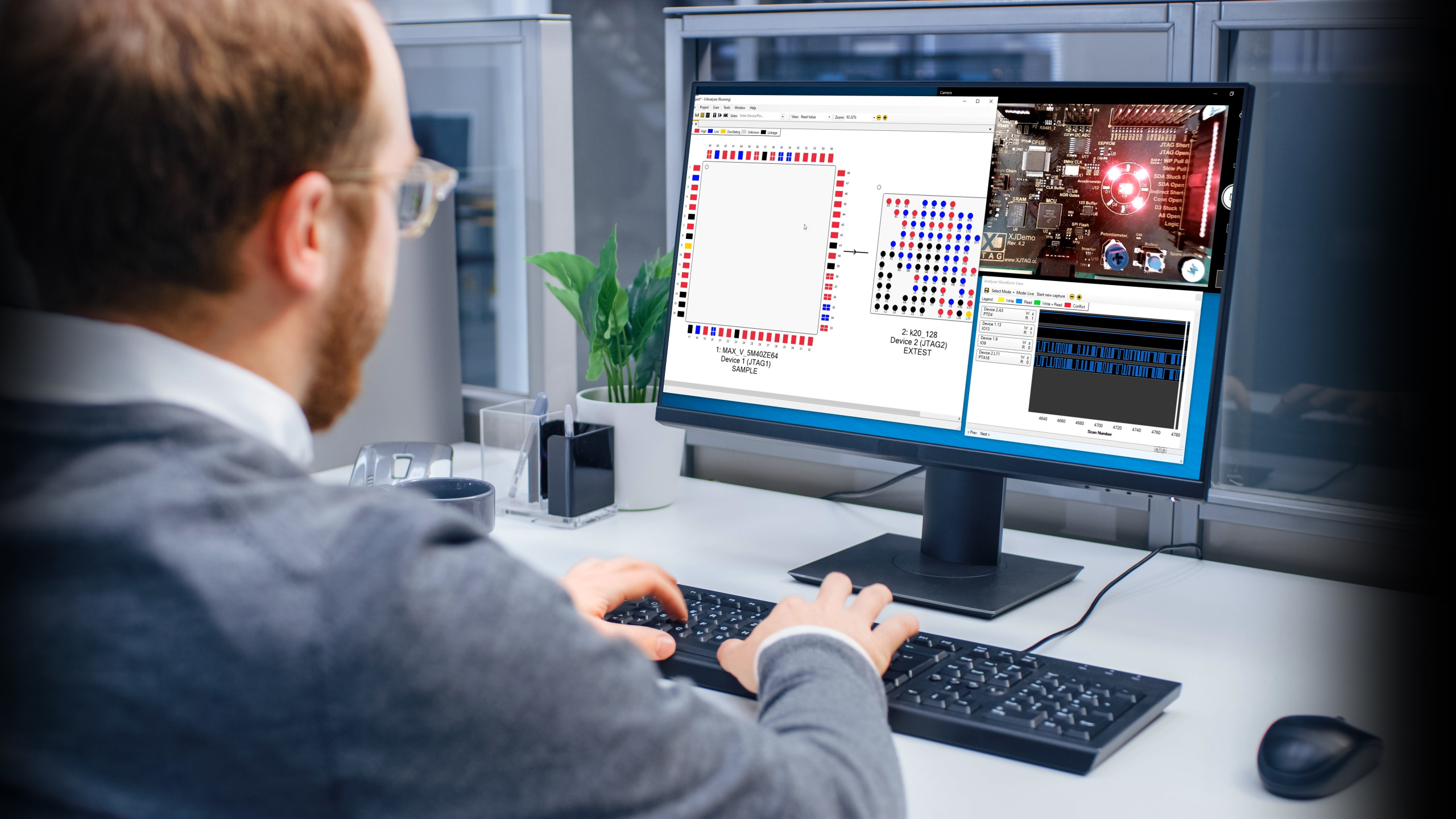

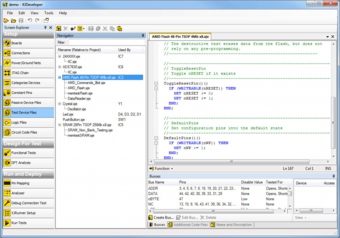

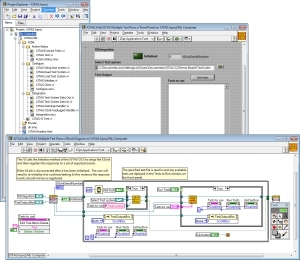

XJTAGのテストを実行する標準インターフェースはXJRunnerです。これは、使いやすいグラフィカルなランタイム環境です。しかしながら、JTAGバウンダリスキャンテストは、他の多くのテスト環境に統合して実行することもできます。XJIntegration APIを介して、他のソフトウェアからXJRunnerおよびXJAnalyserの機能にアクセスすることができます。

XJIntegration

XJIntegrationは.NET DLLであり、他の.NETプログラムがXJPackファイル(XJRunnerのプロジェクト)を開いてテストや関数を実行したり、XJAnalyserの機能を使用して個々のピンの値を制御または読み取ることができます。また、他社の検査環境内にXJRunnerのテスト出力ウィンドウなどを埋め込むこともできます。もちろん、テスト結果は、呼び出し元のプログラムによって簡単に取得でき、より大きなテスト環境の一部に統合できます。

National Instruments – LabVIEW / LabWindows CVI / TestStand

National Instruments™のLabVIEW™は、ハイブリッドなテストシステムを構築するための最も一般的なシステムの1つです。XJTAG Virtual Instruments(VI)とTestStand™シーケンス(XJIntegrationに基づく)のフルセットは無料で利用できるため、XJTAGのテストをLabVIEWまたはTestStandテストシステムにすばやく簡単に統合できます。

これらのテストは、独立して実行することも、他のテスト機器とやり取りすることもできます。National InstrumentsのLabWindows™/ CVI™は、ANSI Cで記述された独自のテスト環境にさまざまなテスト技術を簡単に統合する機能を提供します。XJTAGのテストは、付属のWindows標準プログラミングインターフェイス(.NET)を使用して、CVIテストシステムの一部として実行できます。

独自のテスト環境

独自のテスト環境からJTAGテストを実行する場合は、XJIntegration .NETインターフェースを使用したプログラムでテストを制御できます。参照できるC#で記述されたサンプルアプリケーションが、XJTAG開発システムのインストール内にあります。

ATEの統合

XJTAGは、テストカバレッジを最大化し、かつテスト時間を短縮するために、様々な機器ベンダーとの高度なレベルのソフトウェア統合機能を備えています。

特に、SPEAのLeonardoシステム、TakayaのAPT-1400Fソフトウェア、およびKeysightのBTBasic環境との統合により、XJTAGと他のテストシステム間の高度な相互作用が可能になります。

コマンドラインアクセス

XJRun(XJRunnerのコマンドラインバージョン)はXJTAG開発システムの一部で、XJTAGのテストを他のソフトウェアからコマンド実行することができます。

XJRunは、XJTAGのテストセットアップ内で個別のテストまたはテストのグループを実行するように構成できます。XJRunから返された値を使用して、制御ソフトウェアの機能に応じて、単純な結果(成功/失敗)、あるいはエラーの詳細情報をレポートします。

ハードウェアの統合

XJTAGは、ICTなど他のさまざまなテスト機器に物理的に統合して、完全に統合されたテストステーションを構築することもできます。

自動テスト装置(ATE)マシンには多くの種類があり、XJTAGと統合できるレベルも数多くあります。ATEマシンとの統合は、ハードウェア、ソフトウェア、またはその両方で行うことができます。

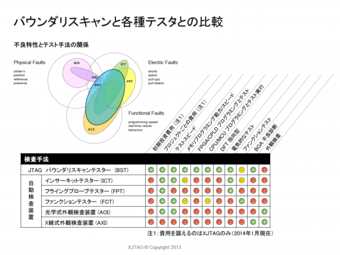

主なATE手法は次のとおりです。

- インサーキットテスト(ICT)

- フライングプローブテスト(FPT)

- ファンクショナルテスト(FCT)

- 自動光学検査(AOI)

- 自動X線検査(AXI)

XJTAGは、いくつかのICTおよびFPTベンダーとハードウェア統合されており、それら専用のJTAGコントローラーカードを、ICTまたはFPTマシンの内部、通常は拡張モジュールスロットに挿入します。これらのベンダーのほとんどはソフトウェアも統合もされていて、1つのシステムが他のシステムを呼び出してテストを実行したり、信号を1つのシステムから駆動して別のシステムから読み取ったりする完全統合テストを実行する機能を提供し、XJTAGが統合テスト中にフライングプローブの位置を制御できるようにします。

特定のソフトウェアとの統合が用意されていない場合でも、ほとんどのシステムは外部プログラムを実行できるため、XJTAGとの統合は容易です。他のシステムはXJTAGのXJRunコマンドラインプログラムでテストを実行し、結果を受け取ることができます。同様に、XJTAGは外部プログラムを呼び出して、その結果を読み取ることができます。また、他のベンダーの.NET DLLをロードして、直接テスト機能を実行することもできます。

サポートされるATE機器

XJTAGには現在、次の統合ソリューションがあります。

- SPEA – ICT and flying-probe machines(analog and digital)

Using either XJLink2 or XJLink2-3030 JTAG controllers

- Keysight (Agilent) – i3070 ICT machines

Using XJLink2-3070JTAG controller

- Teradyne – TestStation ICT machines

Using XJLink2-CFMJTAG controller

- Takaya – APT-1400F flying probe systems

Using XJLink2+ JTAG controller with custom I/O expansion card

JTAGバウンダリスキャンはシリアルで動作することから、通常、大きなフラッシュメモリへのプログラミングは非常に遅いのですが、フラッシュメモリに接続されるプログラマブルロジックデバイス(FPGAなど)があれば、XJFlashを使用して、プログラミング速度を劇的に上げることができます。

XJFlashは、基板に搭載されるFPGAの内部回路を使用して、シンプルなフラッシュプログラマーを構成します。これにより、帯域幅が制限されたJTAGスキャンチェーンの制御、アドレス、データビットのシフトなどの反復的なタスクから解放されます。スキャンチェーンからトラフィックを削除することで、XJTAGは、フラッシュメモリの理論上の最大プログラミング速度に迫ることができています。

XJDirect

すべての基板設計に都合良くプログラマブルロジックデバイスが搭載されていませんが、多くの場合、プロセッサを介してフラッシュメモリにアクセスできるでしょう。その場合、XJDirectを使用して、プロセッサのデバッグポートにアクセスし、プログラミング速度を大幅に改善できます。

JTAGの速度が問題になる場合は、プログラミング速度の改善策は、特定の設計やアプリケーションに依存します。最良の解決策を得るために、XJTAGにまでご相談ください。

XJDirect_FAQ

XJDirectは、従来のバウンダリスキャン技術を使用できない場合に、JTAGを介してフラッシュメモリをプログラミングすることや、基板テストのある側面を実装する高度で革新的なツールです。

ほとんどの場合、XJTAGを使用して、IEEE規格1149.xに準じたJTAGバウンダリスキャンテストで優れたカバレッジを得ることができるでしょう。ただバウンダリスキャンでカバーできないこともあります。そのような状況で、XJDirectはJTAGを介してバウンダリスキャンでは満たされない領域をカバーします。

概要

XJDirectが必要になるケース:

- インターフェースを基板のノーマル動作速度でテストしたい

- 内蔵/外付けフラッシュメモリを高速にプログラミングしたい

- バウンダリスキャンにアクセスできない、または不十分な場合のテスト

これらはXJDirectの3つの異なる側面でサポートされます。

- プロセッサエミュレートテスト

- プロセッサエミュレートプログラミング

- プロセッサ加速プログラミング

プロセッサエミュレートテスト(PET)

PETは、インターフェースを基板のノーマル速度で動作させる必要がある場合、またはデバイスへのバウンダリスキャンアクセスが不十分な場合に使用します。その使用例は次のとおりです。

1:プロセッサにDRAMインターフェースがあるが、バウンダリスキャンを使用してクロックにアクセスできない。

プロセッサの内部レジスタにアクセスして、DRAMへのインターフェースを構成します。インターフェースは、プロセッサから読み取りと書き込みを発行することによってテストされます。

2:プロセッサには、バウンダリスキャンからアクセス可能な1線式インターフェースがあるが、タイミング要件がありバウンダリスキャンではインターフェースをテストできない。

プロセッサの内部レジスタにアクセスして1線式インターフェースを構成し、プロセッサインターフェースを使用して1線式インターフェースを使用した読み取りと書き込みを行います。

3:プロセッサには、アナログモードまたはデジタルモードで構成できるピンがある。

バウンダリスキャンはデジタルモードでピンを使用しますが、インターフェースはアナログモードでテストする必要があります。プロセッサの内部レジスタを使用して、ピンをアナログモードに設定し、再びプロセッサの内部レジスタを使用して、アナログ値を読み取ってチェックします。

4:プロセッサにはDDRインターフェースがあり、バウンダリスキャンよりも速い速度で実行する必要がある。

プロセッサの内部DDRコントローラーが構成され、プロセッサを介して発行される高速読み取りおよび書き込みを使用してインターフェースがテストされます。

5:接続テストを正しく実行するために、プロセッサのI/Oピンのプルアップとプルダウンを有効にする必要がある。

それらピンは、プロセッサの内部レジスタにアクセスすることによって構成されます。

プロセッサエミュレートプログラミング(PEP)

PEPは、プロセッサ内部フラッシュ、および外部にペリフェラルとして接続されたフラッシュメモリの両方のプログラミングに使用されます。

内部フラッシュメモリのプログラミング

上記のPETソリューションと非常によく似た方法で、デバイスの内部レジスタにアクセスし、フラッシュを消去、プログラム、および検証します。

外部フラッシュメモリのプログラミング

バウンダリスキャンを使用した外部フラッシュメモリのプログラミングは、バウンダリスキャンのシリアル動作の性質により、特に外部デバイス自体がシリアルデバイスである場合、時間がかかります。プロセッサの内部レジスタにアクセスすることにより、外部ペリフェラルインターフェイスを構成して、外部フラッシュメモリへのアクセスに使用できます。その後、バウンダリスキャンでは実現できない速度で外部フラッシュをプログラムおよび検証できます。

プロセッサ加速プログラミング(PAP)

ほとんどの場合、PETとPEPは適切な速度性能を提供します。ただし、さらに高速なパフォーマンスが望ましい場合もあります。

多くのプロセッサは、JTAGインターフェースを使用して実行中のコードと通信するメカニズムや、メモリを読み書きする非常に効率的なメカニズムが提供されます。 XJDirectはこれらの機能(デバッグ用の機能)を利用して、非常に効率的なフラッシュプログラミングを提供します。XJDirectは一時的なアプリケーションイメージを使用してプロセッサを構成します-事実上、それを専用のフラッシュプログラマにします。次に、プロセッサによって提供される効率的なメカニズムを使用して、プログラミングデータをプロセッサに転送し、プログラミング速度を劇的に向上させます。

サポートされるCPU

対応実績

以下、XJDirectでサポートされるデバイスの一部です。このリストは定期的に更新されています。デバイスがリストにない場合は、XJTAGにお問い合わせください。

よくある質問

General

Q:XJDirectは、従来のバウンダリスキャンを使用したプログラミングよりも何倍も速くできますか?

A:通常のバウンダリスキャンでは、信号を変更するたびに、JTAGチェーン全体で1つの完全なテストベクターをスキャンする必要があります。ほとんどのプロセッサのデバッグ機能は、JTAGインターフェースを使用してメモリを効率的に読み書きする機能を提供します。XJDirectはこれらの機能を使用してプログラミングデータをプロセッサに送信し、プロセッサ自体がフラッシュをプログラミングします。

Q:すでに高速フラッシュプログラマを使用していますが、XJDirectは検討に値しますか?

A:XJDirectなら、単一のJTAGツールを使用して、1ステップでプログラミングとバウンダリスキャンテストを行えるので、製造ラインで複数のツールを交換する手間が無くなります。またインシステムプログラミングを行えば、フラッシュメモリを事前にプログラムする必要がなく、常に最新のイメージを利用できます。そして、開発、製造、および修理に同じツールを使用できるので、関係者間の協調作業を改善します。

Technical questions

Q:どのフラッシュメモリがサポートされていますか?

A:XJDirectは、パラレルとシリアルの両方で幅広いNANDおよびNORデバイスをサポートしています。

Q:リストにないタイプのデバイスをプログラムしたい場合はどうなりますか?

A:XJDirectでプログラム可能なデバイスは随時追加されています。現在リストされていないデバイスを検討されている場合はお問い合わせください。

Q:どのプロセッサがサポートされていますか?

A:XJDirectは既に様々なデバイスをサポートしています。デバッグインターフェースの情報が得られるなら、殆どの場合、対応可能です。

Q:すでに設計した基板でXJDirectを使用できますか?

A:はい。JTAGポートとその他のデバッグ関連ピンが接続可能なら問題ありません。

Q:フラッシュメモリが基板上のプロセッサに直接接続されていません。それでもXJDirectを使用できますか?

A:はい。プロセッサがフラッシュメモリにアクセスできるならプログラミング可能です。

Q:それぞれが独自のフラッシュメモリを備えた複数のPCBを同時にプログラムできますか?

A:はい– XJDirectは一連の製造検査プロジェクトとして追加できるので、並行プログラミングは並行バウンダリスキャンテストとまったく同じ方法で実装できます。

Q:XJDirectを大量および少量/多品種の製造状況の両方で使用できますか?

A:はい。XJDirectは製造検査プロジェクトに組み込むことができます。またテスト対象基板に搭載されるプロセッサの機能を利用するので、設計が異なる基板に切り替えるときにハードウェアの変更はありません。

Q:FPGAを介した高速フラッシュプログラミングをサポートしていますか?

A:はい– 詳細はXJFlashをご覧ください。

Q:XJDirectを使用してプロセッサの内部フラッシュをプログラムできますか?

A:はい–関連情報(通常はデバイスのリファレンスマニュアル)が利用可能である限り、XJDirectは幅広いプロセッサの内部フラッシュをサポートできます。

Consultancy

Q:XJDirectには追加料金がかかりますか?

A:幅広いプロセッサへの対応と、アプリケーションごとに異なる構成があるため、XJDirectを構成するには少額の追加料金がかかる場合があります。費用については、お問い合わせください。

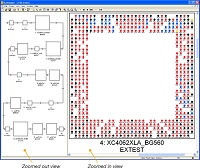

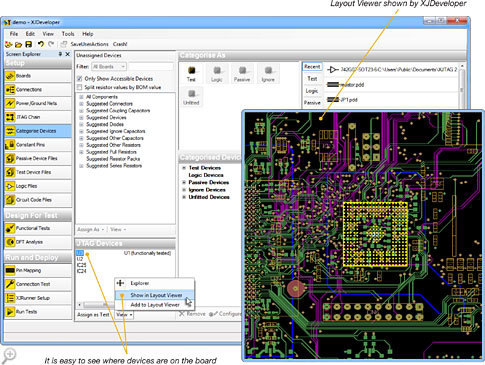

Layout Viewer により基板上の部品やネット、ピンの物理的な場所を即座に特定。ODB++ ジョブから抽出されたレイアウト設計データの表示をするこの機能は、XJDeveloper、XJInvestigator と XJRunner の両方で活用いただけます。

Layout Viewer によりテスト実行時に見つかったあらゆる欠陥をビジュアル表示。Connection Test の結果出力に含まれるリンクをクリックすることで、関連する全ての回路エレメントをダイレクトに表示します。

主な効果

- 修正が必要な欠陥箇所の的確なビジュアル表示で解析作業を支援

機能

- グラフィック表示を、クリップボード、ファイル、プリンタにエクスポート

XJDeveloper、XJInvestigatorとXJRunner に標準装備

欠陥箇所の特定を直ちに行えるLayout Viewerは、XJDeveloper、XJInvestigator と XJRunner に標準装備しています。

回路エレメントの可視化

高度なグラフィカル表示で、選択された部品やネットをハイライト表示。個々のレイヤー表示をオン・オフさせて、特定の回路エレメントを見ることも簡単です。

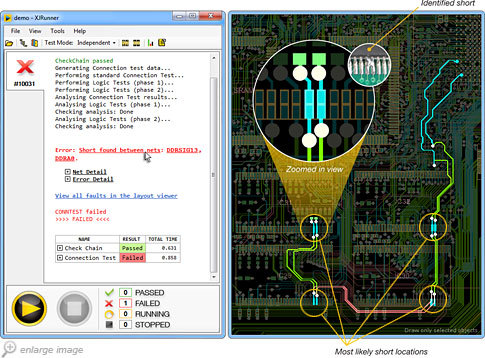

欠陥箇所を直ちに特定

Layout Viewer により、テスト対象基板の欠陥箇所を素早く特定することができます。

XJRunner のテスト結果(テキスト形式)から欠陥のタイプや関連するネット情報が得られます。そしてリンクをクリックするだけで、欠陥箇所をLayout Viewer に表示。 Layout Viewer で欠陥を含んだネット経路を視覚的に確認すれば、問題の特定も容易です。

以下の例では XJRunner による Connection Test に失敗があった相互に短絡している2つのネットが特定されています。ここでレイアウトを確認することで、メモリーデバイス上の4箇所のパッドが最も可能性 が高いことが容易に判断できます。例えばBGAデバイス部分(図右上)では、これらネットのピンが隣り合っていないことが見えるので、欠陥の可能性は低い と判断することができます。

そして基板上の4箇所を詳しく調べることで、IC31のハンダ不良に問題があることを直ちに判明しました。

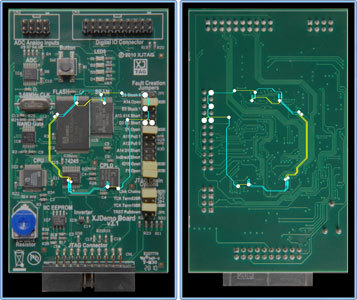

基板写真のインポート

基板上の欠陥箇所を特定するために、基板表面と裏面の写真をインポートして活用することもできます。これらのイメージは、部品やネットをハイライト表示しているCAD データの後ろに表示されます。

回路図ビューア(Schematic Viewer)を介して、XJTAGから回路図上の配置を確認することができます。XJDeveloperとXJRunnerに組み込まれており、XJDeveloperでテストプログラムを設定中に任意のデバイス、ネット、ピンから起動することや、XJRunnerによるテスト結果からのリンクとして、回路図を参照しながら、テストの開発や結果の調査を効率的に行えます。

回路上のデバイスを即座にリンク表示させることで、欠陥検出やテストのデバッグ作業を支援。インテリジェントなネットリスト検索で回路図の関連するセクションを強調表示することもできます。

主な効果

- テスト開発・設定、プロトタイプ基板や量産検査時のテスト結果のデバッグ作業を加速

機能

- XJDeveloper と XJRunnerに標準装備

- ピン、ネット、デバイスの該当箇所を直ちに検索・表示

*検索可能なPDFドキュメントが必要

XJDeveloperとXJRunner に標準装備

回路図ビューア(Schematic Viewer)は、XJDeveloper と XJRunnerに標準装備されています。

Safe and secure

事前にXJDeveloper(テスト開発環境)から回路図情報をエクスポートさせることで、製造検査でXJRunnerから回路図ビューア (Schematic Viewer)を起動することができます。逆にXJRunnerへエクスポートしなければ、もし回路図情報を社外秘扱いにすることできます。

Find the right device, net or pin in seconds

JTAGテストプログラムの設定や基板のデバッグなど、回路図上でデバイス、ネット、特定ピンの検索は欠かせませんが、回路図ビューア (Schematic Viewer)があれば、テキスト検索とPDFのブックマークを活用して、これらの作業が効果的に行えるようになります。

JTAGテストプログラムの全設定段階で、シンプルなコンテキストメニューのクリックから、直ちに回路図上の該当箇所を表示できます。例えばテスト のレビューを支援するDFT(Design For Test Analysis)ツールによるカバレッジ解析にも活用頂けます。

そして初版のボードへのテスト実行結果から、問題と疑われる箇所を回路図上で確かめることができます。そして実基板上のハード的な欠陥なのか、部品が搭載されていないなどの構成上の問題なのかを切り分けることができるでしょう。

更にデバイスが基板上に正しく搭載されていることをチェックするなら、XJTAG Layout Viewerのレイアウト表示機能を活用して物理的な配置をピンポイントに特定できるでしょう。

Generic data import

あらゆる回路図ツールから生成される、標準的なPDF形式のドキュメントをサポート。

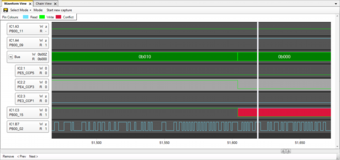

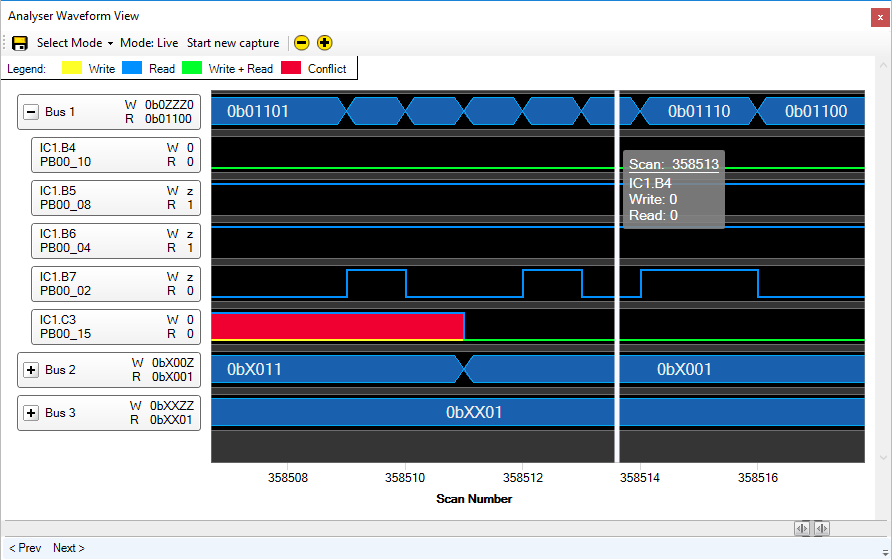

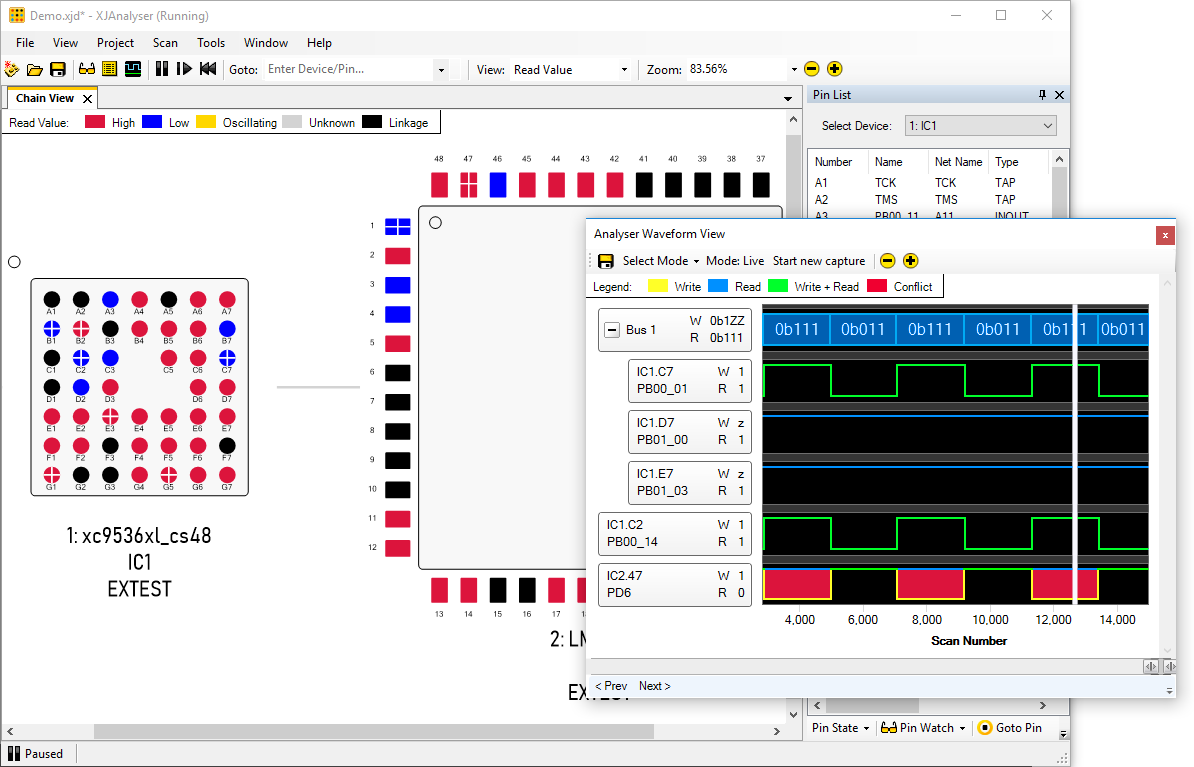

Waveform Viewerは、デバッグや障害診断にユニークな洞察を提供します。データをデジタル波形で表示することで、ライブにJTAGチェーンデータの相関ビューを観測できます。

バウンダリスキャンは信号遷移をリアルタイムでキャプチャすることはできませんが、Waveform Viewerはスキャンチェーンによってキャプチャして、ロジックアナライザタイプのビューでシステムのデジタルアクティビティを表現します。これにより、デバッグおよび障害診断を強化します。

Waveform Viewerは、XJAnalyserの標準機能であり、XJInvestigatorやXJTAG開発システムにも含まれます。

主な効果

- デジタルデータをグラフィカルに視覚化

- 一時的な障害をキャプチャ

- 信号のグループを値として表示

- 定義可能なトリガー条件下でデータを捕獲

機能

- 異なるデバイスからでも、個々の信号の相関をライブに波形で観測

- 信号を任意にグループ化してバスを形成

- 論理レベルの組み合わせまたは信号の立ち上がり/立ち下がりエッジに基づいて、単純または複雑なトリガー条件を設定

- アドレスおよびデータバスを自動的にデコードして、それらの値を2進数、10進数、または16進数の値として表示

- 同一期間にキャプチャされた複数信号からロジックレベルをスキャンして間欠障害の解析を支援

- 分析または比較のためにデータをファイルに保存

Waveform Viewerは、従来のロジックアナライザーにある多くの機能をバウンダリスキャンの領域にもたらします。

Waveform ViewerとXJAnalyserを組み合わせることで、デジタル信号をグラフィカルに制御・観測して、デバッグや障害診断効率を大幅に改善します。

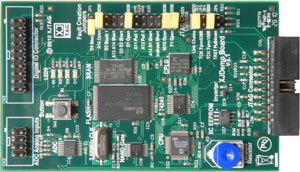

XJDemoは、XJTAG製品の理解を促進する為に使用可能な、完全実装のデモ用基板です。

XJDemoはXJTAGのソフトウェアと一緒に無償で提供されます。また、XJTAGの全ての機能をデモする為の日本語チュートリアルも含まれています。

XJDemoボードには以下の部品が搭載されています:

- デバッグ用のジャンパーピン(短絡と断線をシミュレート可能)

- JTAG 用コネクタ ( XJLink / PXI )

- 2種のSVFフォーマットのサンプルアプリケーション

- 回路図

- BSDLファイル、ODB++フォーマットのネットリストファイル/layout data

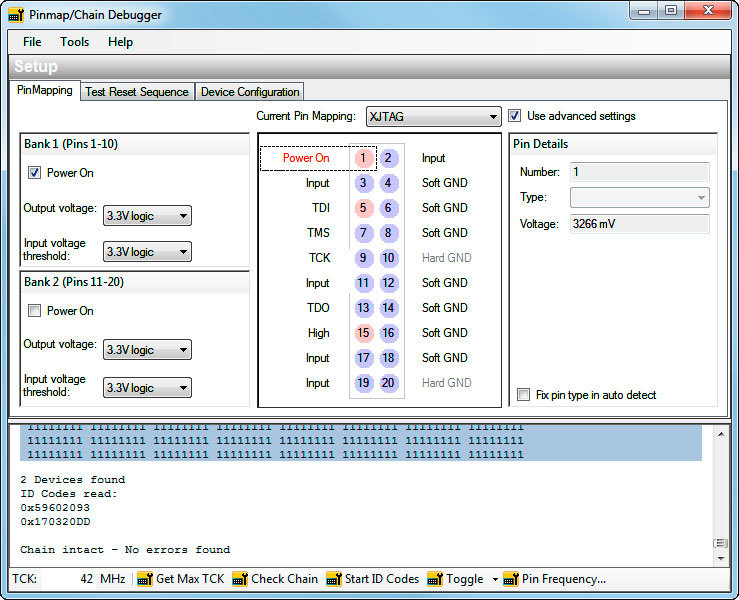

すべてのXJTAG製品にインストールされるJTAGチェーンデバッガーは、JTAGチェーンのトラブルシューティングに役立つ強力なツールです。JTAGチェーン上のデバイスを操作して、障害箇所を自動的に特定します。さらに調査が必要な場合、さまざま機能を駆使して、問題の原因を突き止めることができます。初期のプロトタイプボードでのJTAGチェーンのデバッグから、製造ラインで発生した問題の解決まで、製品ライフサイクルのすべての段階で使用いただけます。

破損したJTAGチェーンのデバッグだけでなく、JTAGチェーン内のすべてのデバイスに対して正しいBSDLファイルが割り振られていることも検証します。これにはIDCODEのチェックに加えて、バウンダリスキャンレジスタの長さの照合を行います。

そしてJTAGチェーンが機能することを確認できれば、XJTAGの各種機能を用いて、基板の検査を直ちに開始できます。

主な効果

- 複数のJTAGチェーンの構成を簡単にセットアップ

- JTAGチェーン内の障害箇所をすばやく特定

- 障害のあるJTAGチェーンを調査するためのシンプルなツール

機能

- JTAGピンの現在の状態を表示

- ピンの電圧と周波数を測定

- JTAG信号の配置変更・設定が容易

- IDCodeとバウンダリスキャンチェーンを確認

- JTAGチェーンの最大周波数をチェック

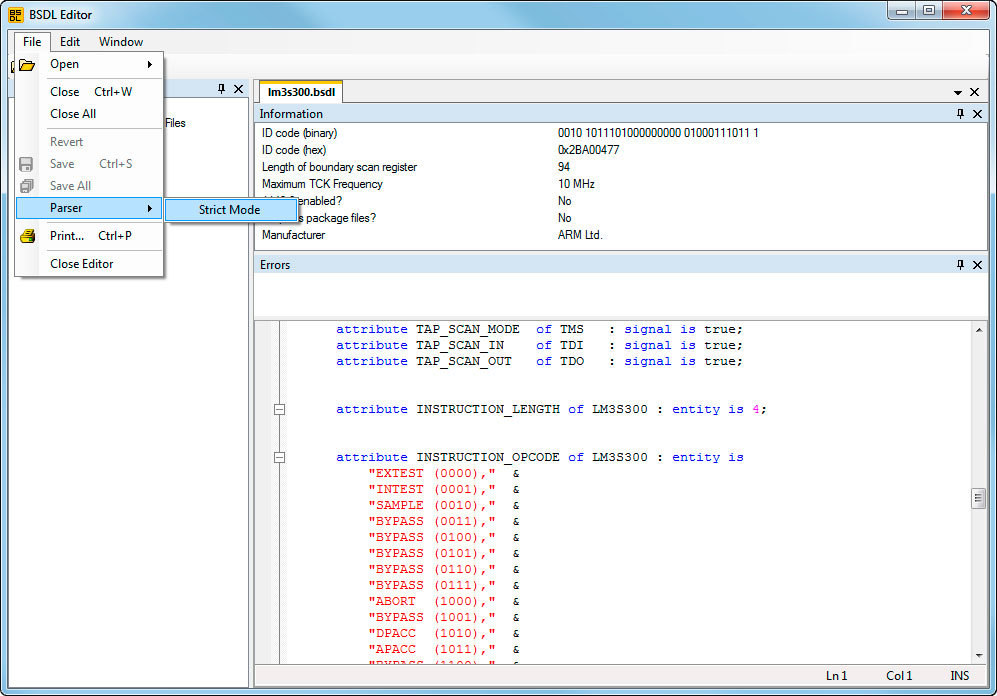

BSDLエディターは、XJDeveloper内でBSDLおよびカスタムセルタイプパッケージのファイルを表示および編集できます。

エディターには、IDCODE、TCK周波数、バウンダリスキャンレジスタの長さ、デバイスの製造元など、BSDLファイル内の情報の概要が表示されます。

メインファイルエディターには構文の強調表示があり、キーワードをさまざまな色で表示して読みやすくしています。エディターは「コードの折りたたみ」もサポートしています。コードのブロックは、左マージンの「-」記号をクリックして折りたたみ、「+」をクリックして再度展開できます。

「厳密な解析モード」でのBSDLファイルの検証

独自のBSDLファイルを作成する場合は、「厳密な解析モード」を有効にして構文エラーを特定することができます。これはBSDLファイルの読み取りに使用するパーサーが、BSDLファイルをIEEE 1149.x仕様に対して厳密に解釈します。識別されたエラーはすべて、エディターの「エラー」セクションに表示されます。

JTAGを使用して基板をテストするには、通常、ネットリストを含む設計情報が必要です。ただ殆どの場合、修理を担当する技術者はこのデータを入手できません。このような場合でも、XJTAGには特別に設計された機能があり、JTAGバウンダリスキャンテストを利用できます。

ネットリストがない? 問題ありません!

テストしたい基板のネットリストがない場合でも、XJDeveloperでネットリストを使用せずに、基板上のJTAGデバイスのBSDLファイルに基づいてテストを作ることができます。一部のデバイスのBSDLファイルがない場合でも、最小限のBSDLファイルを生成することもできます。システムは、接続テスト中に使用するJTAGデバイス間の接続を、動作しているボードから自動的に学習できます。またテストカバレッジを拡張するために、RAM、フラッシュメモリ、I²CやSPIなどのペリフェラルバス上のデバイスなどのJTAG以外のデバイスを追加することもできます。

迅速な修理を支援

この機能は、ネットリストが提供されない基板の修理に役立てられます。以前ならネットリストの提供を待たなければならなかった、あるいはバウンダリスキャンの使用を諦めざるを得なかった状況でも、直ぐにテストを開始できます。この機能が有るXJTAGバウンダリスキャンテストツールは、修理業界にとって非常に重要な選択肢の一つです。

非JTAGデバイスを追加してテストする

'no-netlist'機能を使用すると、基板上のJTAGデバイスへの接続方法を指定するだけで、非JTAGデバイスをテストプロジェクトに追加して、XJEaseライブラリファイルを使用してテストできます。これにより、テストカバレッジが向上し、物理的なプローブ接続を駆使してテストするのに必要な時間と労力を節約できます。

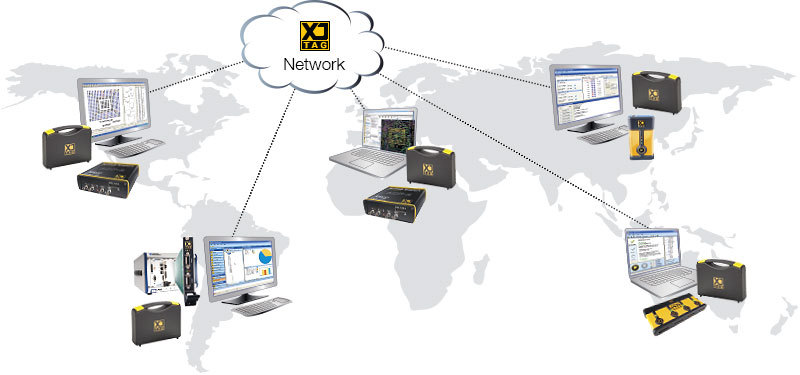

ネットワークライセンスは、ハードウェアプローブ内に書込まれるライセンスの代替手段で、ネットワーク上のどこからでもXJTAGソフトウェアを利用できるようにします。必要なときにいつでもツールを使用できるので、生産性と効率を高めることができます。

主な効果

- 必要なときに必要な場所でXJTAGを起動して生産性と効率を改善

- 製造ラインと設計エンジニアでライセンスを共有して費用を削減

ネットワークライセンスを選択する理由

ネットワークライセンスは、XJTAGのライセンスをグローバルな規模で管理する簡単でコスト効率の高い手段です。プローブ本体を移動させる必要がないので、あらゆる場所でXJTAGを最大限に活用できるようにします。

コストを最適化

異なる製品の複数の製造ラインまたは開発チームが、各々ライセンスを持つ必要はありません。ライセンスが同時に必要になる最大数を共有して、必要に応じて割り当てるだけです。

使用量を最大化

異なるチーム間でソフトウェアを共有することで、XJTAGの使用効率を最大化します。隣の開発チーム、同じ敷地内の異なる事業部、他の国でも、開発と製造部門で、同じツールを共有できます。

どのように機能しますか?

XJTAGのソフトウェア機能の各ライセンスは、ネットワークライセンスサーバー、またはテスト対象基板へ接続するJTAGプローブ本体に保持されます。 ライセンスを保持するXJLink2など小型のプローブ本体は持ち運びに便利ですが、ネットワークライセンスでその範囲をさらに拡張します。設計エンジニアから修理技術者まで、XJTAGのライセンスをサーバーからチェックアウトして、必要なソフトウェアを実行できます。

例えばテストのセットアップだけなら、ネットワークライセンスを使用して、ターゲットハードウェアにJTAGプローブ本体を接続せずに行えます。テストの実行には、JTAGプローブ本体を接続し、ネットワークライセンスを使用します。使用を停止すると、ライセンスはサーバーに解放され、組織の他の場所で使用できます。

ネットワークサーバーにライセンスを保持することで、特定の場所に固定されなくなります。そして組織内のすべてのユーザーが、XJTAGのテスト機能にアクセスできます*。

*基板に接続するJTAGプローブ本体は必要です。

何を使っているのか?

XJTAGのネットワークライセンス管理には、Flexera Software社が提供するFlexNet Publisher(旧FLEXlm)を使用しています。

FlexNet PublisherおよびFLEXlmは、Flexera Softwareの商標です。

XJAPI ソフトウエア & ハードウエア間インターフェイス

XJAPI により、XJLink やPXI ハードウエアプローブからJTAG チェインに対して、ローレベルアクセスができるようになります。これにより、開発基板、評価ボード、テストシステムなど各種システムへの統合が容易になります。

高速USBを搭載するJTAGハードウエア(XJLink / XJLink2)から、アプリケーションプログラミングインターフェイス(XJAPI )を用いて、JTAGチェインを直接制御します。

あるいは、高速PXI に搭載されたJTAGハードウエア(PXI-01)から、アプリケーションプログラミングインターフェイス(XJAPI )を用いて、JTAG チェインを直接制御します。

XJTAGのバウンダリスキャンテストツールは、プロトタイプの開発・デバッグから製造検査や不良解析までシームレスに利用されることが特徴のひとつです。そしてフォールトディクショナリにより、既知の欠陥情報が関係者間で共有され、不良解析等の作業が支援されます。

開発技術者と製造技術者で情報共有

フォールトディクショナリは、基板固有の情報を簡単に格納して共有できるので、プロトタイプと製造現場の橋渡しを効率良く支援します。また障害が発見されたときにディクショナリに追加することで、製造段階でも継続的に情報を更新できます。

プロトタイプの立ち上げ時および製造工程の検査中に収集されたデータを登録して、後のテストで同様の障害が検出されたときに、診断を自動的に提案します。障害は、単一のテストが失敗するだけの単純な場合もあれば、多数の関数からの戻り値の特定の組み合わせに依存することもあります。

フォールトディクショナリで定義された基準を満たすテスト実行中に検出された障害条件により、自動的に障害定義がテストオペレーターの画面に表示されます。このメッセージは、基本的なユーザーに必要に応じて指示を出し、さらに重要なことに、修理担当者が基板上のさまざまな障害の場所を迅速かつ効率的に特定するのに役立つ詳細な情報を提供します。

フォールトディクショナリは、XJTAGプロジェクトを安全に格納するXJPackファイルの一部として製造検査環境に渡されます。XJPackファイル自体は編集できませんが(システム設計者が指定したテストと監査が実行されることを保証するため)、テスト開発時または製造現場でフォールトディクショナリは編集されます。それらの経験から障害または障害の特定の組み合わせを指摘します。障害発生時に文書化することで、製造検査時の障害調査の作業が大幅に軽減されます。そして、基板のスループットが向上し、歩留まりが改善します。

主な効果

- 開発チームと製造チームの情報を共有する簡単な手段

- 迅速な故障診断を可能にし、製造検査のコストを削減

- 定義された障害コンディションに基づいて調査を支援

機能

- XJDeveloperでXJRunnerのテスト実行用XJPackファイルを生成時に制限なく障害を登録

- 既知の障害を修正する方法をテスト担当者に提供

- 障害ごとに複数の基準を持たせることで、誤検知を回避

- 製造検査時に既知の障害の(過去の経験から)考えられる原因を表示

- テストがループするように設定されている場合、障害発生の累計を提供