まず JTAGデバッガとの違いについて

JTAGデバッガは、ソフトウエアのデバッグや書込み、FPGA/CPLD へのインシステムプログラミングに利用されます。本来、IEEE Std 1149.1はバウンダリスキャンテストの規格ですが、その中のJTAG通信プロトコルのみを利用します。JTAG信号を介してデバッグやプログラミング用のレジスタにアクセスできることの優位性が、デバイスメーカに認められたためです。そして多くのソフトウエア技術者によるデバッグやFlashプログラミング、ハードウエア技術者のインシステムプログラミングの需要を満たすことで広く採用されています。

以下の各記事では、バウンダリスキャンテスト技術の基本を紹介します。また、その能力を最大限に引き出すXJTAGの注目の機能についても言及します。

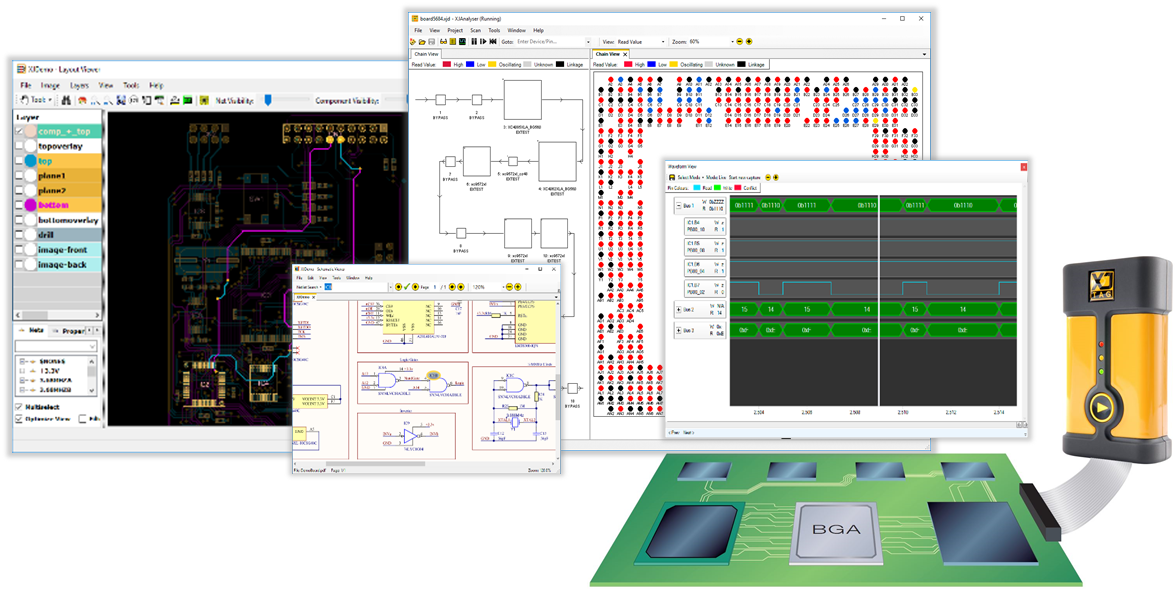

XJTAGのソフトウエアならJTAGテストプログラム開発は容易です。ユーザ側で開発して再利用もできます。

その簡単な手順を動画で紹介します。 日本語字幕を表示できます

ボードデータを入力

ネットリスト、回路図、BOMをインポートする方法と、それに関わるトピックを紹介します。

1 – ネットリストの追加:ネットリストをXJDeveloperにインポートする方法とサポートされている形式について

2 – 回路図の追加:検索可能な回路図ファイルをXJTAGテストシステムに追加する方法

3 – BOMのインポートとデータ型の割り当て:XJDeveloperプロジェクトにBOMファイルをインポートする方法

4 – 内部部品番号とカスタムデータタイプの使用:内部部品番号と非標準BOMデータのインポート

5 – 複数のソースからBOMデータをインポート:ネットリスト、回路図、その他のソースからBOMデータを抽出する方法

6 – 実装していないデバイスの扱い:ボードデータを分析し、どのデバイスを実装していないとマークするかを提案するようにXJDeveloperを設定する方法

7 – プロジェクト間での共有やテストフィクスチャへの考察:プロジェクト間で再利用して作業工数を軽減する方法と 検査治具にテストボードを指定する方法

JTAGインターフェースの設計のコツやヒント、最適な方法を動画で紹介します。 既にJTAGバウンダリスキャンテストに経験があっても、多くの役立つ情報が得られるでしょう。 日本語字幕を表示できます

JTAG バウンダリスキャンセミナー

実践的な内容に、質疑応答が1時間近くになるなど、お陰様でたいへん盛り上がりました。JTAGテストで考慮すべき課題が実践経験をもとに紹介されたことが良かったかと思います。

“容易なテスト生成、故障解析、高速フラッシュ書込みなどXJATG社の高い技術と先進的な取り組みに感心しました。また開発技術者から直接話しを聞けたのは素晴らしいことでした。” ‐富士通株式会社 ものづくり推進本部 シニアエキスパートエンジニアSEE、技術士(電気電子) 亀山修一様(バウンダリスキャンハンドブック の監訳者)